第八章 RCC使用HES/HSI

第八章 RCC使用HES/HSI

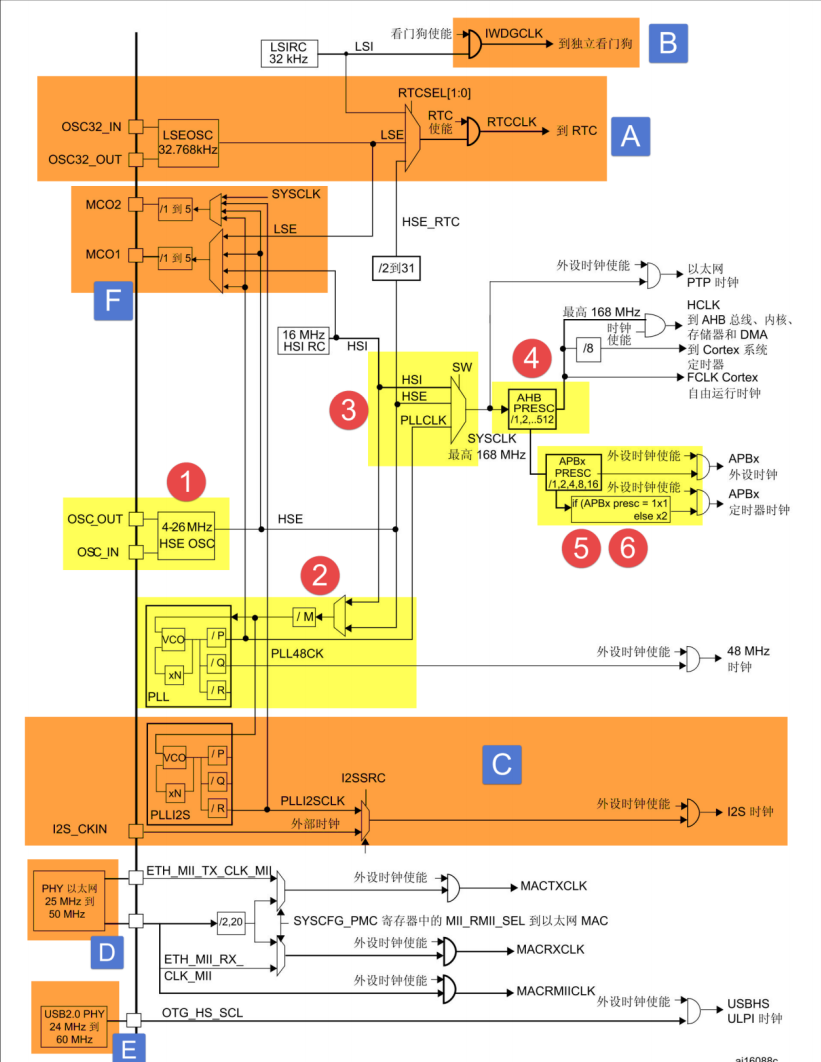

为巽1、RCC主要作用 时钟部分

设置系统时钟SYSCLK、设置AHB分频因子(决定HCLK等于多少)、设置APB2分频因子(决定PLCLK2等于多少)、设置APB1分频因子(决定PLK1等于多少)、设置各个外设的分配因子。控制 AHB、APB2 和 APB1 这三条总线时钟的开启、控制每个外设的时钟的开启。对于 SYSCLK、HCLK、PCLK2、PCLK1 这四个时钟的配置一般是:HCLK = SYSCLK=PLLCLK ,PCLK1=HCLK/2,PCLK1=HCLK/4 。

2、RCC时钟树

库函数时钟系统始终函数:SetSysClock()。

HSE时钟树设置为:

HCLK=SYSCLK=PLLCLK=180M(F429)

PCLK1=HCLK/2=90M(F429)

PLCK1=HCLK/4=45M(F429)

2.1系统时钟

2.1.1

HSE是高速的外部时钟信号,有无源/有源晶振提供,频率4-26MHZ。

有源晶振,时钟从OSC_IN引脚进入,OSC_OUT引脚悬空。

无源晶振,时钟从OSC_IN,OSC_OUT进入,配合谐振电容。

2.1.2 锁相环PLL

PLL的主要作用是对时钟进行倍频,然后将时钟输出到各个功能部分。

PLL和PLLI2S,他们由HSE或者HSI提供时钟输入信号。

主PLL有两路时钟输出,第一个输出时钟是PLLCLK用于系统时钟,F429最高时180M,第一个时用于USB OTG FS的时钟(48M)、RNG和SDIO时钟(<=48M)专门用于PLLI2S生成精准时钟,给I2S提供时钟。

HSE或者HSI经过PLL时钟输出分频因子M(2~63)分频后,称为VCO的时钟输入,VCO的时钟必须在1 ~2M,选择HSE=25M作为PLL的时钟输入,M设置25,VCO输入时钟必须等于1M。

2.1.3 系统时钟SYSCLK

系统时钟来源可以时HSI、PLLCLK、HSE,具体由时钟配置寄存器RCC_CFGR的SW位配置。SYSCLK=PLLCLK=180M。

如果系统时钟是由HSE经过PLL倍频之后的PLLCLK得到,当HSE出现故障的时候,系统时钟会切换HSI=16M,知道HSE恢复正常。

2.1.4 AHB总线时钟HCLK

系统时钟经过AHB预分频器分频之后得到的时钟是叫AHB总线时钟,就是HCLK,分频因子可以是[1,2,4,16,64,128,256,512],具体由时钟配置寄存器RCC_CFGR的HPRE

位设置。片上大部分外设时钟都是HCLK分频德奥,AHB总线的外设设置时使用外设的时候设置。

2.1.5 APB2总线时钟PCLK2

AHB2总线是由PCLK2由HCLK经过高速APB2预分频器得到,分频因子可以是[1,2,4,16],由时钟配置寄存器RCC_CFGR的PRPE2位设置。PCLK2属于高速的总线时钟,片上高速的外设就挂载到这条总线,比如全部的GPIO、USART1、SPI1等。

2.1.6 APB1 总线时钟PCLK1

APB1总线时钟PCLK1由HCLK经过低速APB预分频器得到,分频因子可以是[1,2,4,16],由RCC_CFGR的PPRE2位设置。PCLK2属于低速的总线时钟,最高为45M(F429),片上低速的外设挂载到这条总线上,比如USART2/4/5,SPI2/3,I2C1/2。